fpga+as9361实现qpsk步骤

粉丝1103获赞2710

相关视频

02:01

02:01 03:32查看AI文稿AI文稿

03:32查看AI文稿AI文稿在这个满是摄像头的世界,普通的红外探测器早就瞎了,需要更暴力的手段。这种靠红光反射找镜头的玩具,只能抓抓十年前的低端货,现在的真红摄像头带绿光片,甚至藏在镜面后面,想抓它别找红点, 去抓住他的灵魂。今天我不教你找红点,我要使用雷达技术,让所有隐藏的半导体自己尖叫。我是归机修仙,市面上卖几百块的防拍神器,原理是反光,但这招对针孔镜头几乎无效。专业玩家用的是这个非现行节点探测器, 原理很简单,所以电子产品里都有半导体,只需要我发射一个九百一十兆赫兹的电磁波打过去,半导体就会因为非限性特征,把这个波变异反射回一个一千八百三十兆赫兹的 s 斜波。 墙壁、木头、衣服没有这种反应,所以在我的雷达眼里,只有电子元气件是发光的,这就是物理层面的透视。为了验证原理,我搬出了压箱底的家伙。主控是塞灵斯的 z c u 幺零二,售价几万块的工业级巨兽, 用它来抓摄像头,简直是加特林打文字,这才是极客的浪漫。射频核心是 a d 九三六幺 s d 卡领域的神卡,哪怕没有外置功放,它自己也能输出几毫瓦的功率。 注意看这两根天线,长得像蚊香,但内有乾坤。左手这个是左极化,负责发射。右手这个是右极化,负责接收。为什么要一左一右? 因为我要防止自己发出的信号把自己震聋,这叫极化隔离。这是专业雷达才有的配置,写 python 脚本指示玩具,真正的速度在底层,我直接修改了 f p g 的 逻辑门电路,重新定义了 ad 九三六幺的收发时序, 此时没有加功放,没有加滤波,只有 ad 九三六幺直连天线。这是一款我们之前给客户做的相机,工业相机,然后现在在雷达前面,它的回波信号变得非常强, 然后我们再拿掉它的回波功率,一下减了好多,然后再加上 它的回波,一下又强了好多。 这是我们做的一款视频芯片视频版,然后放在这块,它的回波更强了,比之前的还强好多, 现在已经到了预值的临界点,现在去掉, 还有恢复到很低的状态,再试试 会变得很高,只有五毫瓦的功率。这是近战刺刀模式 相机,没有任何无线信号的发射,甚至都没有通电,但在我的九百一十五兆探照灯下,它无处遁形, 但是现在的距离只有五厘米,在实战中还不够用,这只是原理验证。下一集,我们要给这台机器注入一千倍的能量。装上这套重型装甲,我们要挑战那个被称为绝对屏蔽的终极目标手机。关注我,见证手搓雷达的诞生!

2510硅基修仙 12:18查看AI文稿AI文稿

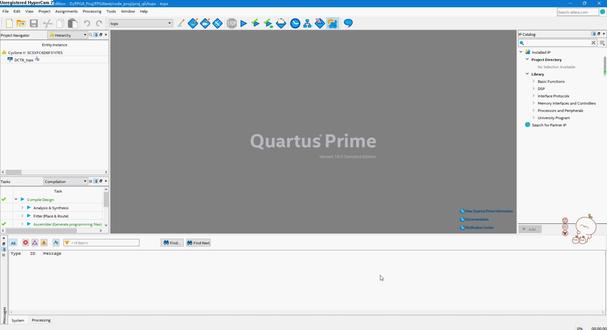

12:18查看AI文稿AI文稿万事开头难,迈出了一步,后面的脚印才会更清晰。本设计 f p g a 采用置顶向下的设计方法,展示了完整的设计功能和实现细节, 下面直接讲解干货。对顶层有问题或者功能有疑问或者设计细节有疑问的朋友可以留言一起讨论,大家共同进步。这里也有我们的联系方式,可以进行私人订制设计,欢迎大家交流讨论, 共同完成设计。好,开始讲解这个 q p s k 的一个调制哈,我们先打开这个科特斯,然后把这个点 q p f 文件直接拖进来就可以了,拖进来之后这里可以选选 芯片啊,芯片选好之后可以配银角,然后这里我们先综合一下看,点开这里 feel 可以看到文件哈,文件在这里,然后采用的是置顶向下的一个设计方法,然后是这里啊顶层, 然后顶层是这里,可以看到是 q p s k 的输出啊,然后这里是 b p s k, 输出的是十比特,然后第一个模块就是产生这个 m 系列吗? m 系列就相当于是一个随机数, 这里的马元素率他要求是五百 k 啊,所以我们重点可以测测一下这里的五百 k, 然后这里是创并转换,这里要转成两比特两比特的, 因为 qpsk 他是两比特,两比特的一个调制嘛,就是相当于是一二三四个象限,然后这里有了这个之后,他就可以来下面这里选啊,选这个调制 波形,上面这个是给的是 b b q s k 的,下面下面这个是 q p s k 的,也就是这里调出来的是 b p s k 的一个调制波形,这里调出来是 q、 p、 s、 k 的波,不一样的是这里进来的数据不一样啊,一个是一比特的,一个是两比特,然后这里是个所向环,所向环要背平得到一个窄波嘛,然后因为我们用了二百五十六个点,所以这里就用二百五十六兆, 二百五十六兆的这个频率就可以了。那我们来看一下这里,这里编译成功哈,编译成功之后,我们可以看到刚刚那个顶层那个关系图, 通过看这个 rtr 就比较清晰啊,就不用去理解那个代码,看这个图就可以得到那个代码那个结果,然后我们跑一下这个反针,反针点这里就能跑下来, 然后反正我们就先让他先跑着哈,他这里先跑着,我们先来看一下代码,那代码,这里看一下 m 系列是怎么产生的,这里是五十兆,五十兆进来的话,这里高电瓶的话就复位哈,这里有个技术机是为了控制马元素率的,五十兆经过 一百个技术之后,那么他就会得到五百 k 啊,就相当于五十兆分频成五百 k 嘛,然后每五百 k 的话,这里就控制这个 m 系列,他就第二次亦或一次啊, 那易获之后,这里要这个要左移哈,就右移哈,就是把高四位放到低四位这样,然后这里移位之后就可以得到那个 结果哈,然后我们将这个,将这个的最低位哈,就是刚刚移位的最低位放到这个 m data 这里输出来,就可以得到一个随机产生的一个 m 序列哈, 啊,这个 m 系列他就从这里就进来了啊,进来到这里他就进行了一个创病转换,然后创病转换这里他要进行一个十六兆的采样吗?系统是因为是五十兆,所以这里拿五十兆去十六兆就得到这个每每次要采样的这个节拍啊, 然后这里再通过这个来采样就行了啊,这里有个控制采样的,在十六兆的速率下进行采样,那每每一次他进来就左一个,左一个,这样就可以把采样得到的数据放在这里啊,因为马原速率 是五百 k 啊,所以我们这里采三十三个就行了,然后每一次拿它中间的值,就是这个采样。 simple, 这个第十五位,第十六位,第十六位,因为它三十二的长度,这里定义它是,所以每次拿十五中间的值就可以拿的比较准,然后把这个值放在这里, 然后这里是左移吗?相当于把低位放到最高位,然后把最低位用产量得了值来补齐就可以了,这样就可以得到一个两比特的数据啊,两比特的数据就从这里输出来啊,输出来之后 说出来之后就来到了这里哈,下面这两个模块就是调制模块,看懂,看懂了这个其中一个,另外两个就懂了。我们先来看一下梁比特,这个梁比特,梁比特这个是这里啊, 这里进来他会这里有四个地址吗?他不一样的是因为,因为他是用那个文件合成的哈,这个波形他一共是有一百二十八个点, 一百二十,一百二十八个点,我们按向位来把它切,就是除以八份,因为他二派吗?除以八份的话就可以得到四分之派,还有四分之三派,四分之五派和四分之七派就正好是四个向位点的位置,就代表了 四种波形的起始点哈,像零跟像前面的 b p s k, 它就只有零和一嘛,就只有零和太两种,也就是也就是这个的零点或者四分 四分之四派那个点啊,就两个地方派,区别就在这里哈,然后我们来看一下啊,这个是存的波形啊,波形就在 步行,就在这里面啊,可以看到点开之后他就按顺序这样数着下来就可以了,一共是一百二十八个, 然后一百二十八个要得到两兆的速率,那么他的每才每一个点的那个频率应该是二百五十六兆嘛,二百五十六兆去除以两兆,那么除出来的结果就是, 呃,二百五十六就除一百二十八,拿这个频率哈,就是这里这个背出来的频率去踩踩每一个 点,每一个点用二百五十六的时钟去踩哈,然后踩了一百二十八个点,合成一个正旋波,这个正旋波就正好是两兆, 然后剩下的我们只要管去控制好这个地址就可以了,这个地址根据书卷的这个 数据做一个四选一就可以了,如果是零零的话,那么就用 data 零啊这个地址去控制,然后一二三,嗯,对着刚说了零的话,它就是在这里,是四分这里哈,八分之一判 这里啊,八分之一派,八,八分之三派,八分之哦,四分之一派,四分之三派,四分之五派,还有个是四分之七派啊,你看这里是成了他的倍率吗? 那么如果是零零,刚才就用 date 零的来加就可以了,那如果不是的话,就保持着这个初始香味,下面也是一样的哈,就是如果是零一的话,那么他就一直在加就可以了,按照这个地址啊,其他的就保持着他的初始香味, 那这样就可以得到我们想要的初始向位的值的一个调项的结果。然后我们看一下这个反针,反正在这里他是一直在跑的话,这里我们可以把 把这么关心的参数给他加进来,像这个像这个随机数产生的,还有个采样后的数据, 还有这个背屏也可以看一下,想看的话,好,这里波形就有了,波形有的话 我们可以把对对照着看起来哈,这里是 q p s k 的哈,然后这个是 b p s k 的,没有数据的话都要复位一下,新加建的边上都要先复位一下,哎,各个模块的仿真都在这里哈, 这里都有哈,想看哪个模块加哪个模块就可以了。然后我们再看一下,这里用的是无符号数啊,我们把它选成无符号数,然后这里再调整一下,就可以看到波形,这里波形就出来了哈, 这个比较短哈,我们再让他多跑长一点时间, 好,这样就能看到这里哈,这里是,这里是零,哈一的话,它是从派开始的, 这里可以看到这里是一个完整的周期,然后如果是零的话,那么他就从零枪位这里开始,到这里就正好是一个拍,这里是二拍嘛。然后我们看一下这个马云是怎么测的, 我们多找点值哈,多找点值, 我们来测一下这个哈,这个他比较突出一点啊,就拿两个这个时间轴来夹就可以了,那夹的话夹的话他在下面哈,这个看一下怎么给你看到, 那这里夹的话就能看到这里调一下就可以了,他就可以大概是五百,这里能看出来哈,就五百 k 嘛,然后看频率也是一样的频率,看窄播的频率,就这样看, 也是接近这个两兆的话,这里可以放大,你放的越大去测的就越准。然后这个彩样是怎么看呢?彩样要去把这个 sample 给它加进去啊, 这里可以看到,让他多跑一下,不然看到的值比较少。 好,这里我们也可以来测,这个 simple 的话也是也也是用同样的方法来测试测就行。 好,这里可以看到这个是在动的哈,然后把它拿过来这里测一下就可以了,这里可以看到也是调整上这个位置就可以把它测的比较准哈,也就放大,这里还没对齐,对齐的话应该就是十六兆。 好,这个代码和反正就是这样的哈,这里是一个 qpsk, 一个香味的变化,这里是零零嘛,零零他是从四分之派的地方开始启动,到到这里他变 变成了零一,零一的话他是四分之四分之三派哈,四分之三派的地方后面这里还有一零四分之七派,这样对对应着去看就可以了。 好,代码和反针就是这样的哈。感谢收听,有问题可以留言与我们联系讨论, 且代码不易,点赞收藏支持一下,有其他想法或者建议也可以留言讨论,大家共同进步,感谢您的支持,谢谢。

01:03查看AI文稿AI文稿

01:03查看AI文稿AI文稿甲方的第一个要求应该是找到办法,然后可以实现了一个信号扩展出很多很多很多很多个信号,来试一下啊。我现在是这一个按键,对了很多很多条线按这个按键, 哎,按错了按错了,哎。按一下 那么飞的更快,达到两点五兆的速,那么 fga 上这一个输入引角就可以同步传出去了。 哇,就这几行,就这四行。 fga 啊,果然是神啊,太牛了哦吼吼吼。

37自造工厂 22:26查看AI文稿AI文稿

22:26查看AI文稿AI文稿嗯,昨天有粉丝啊留言说,呃,讲一讲持续约束啊,因为可能之前参考的一些教材里或者是资料里对于持续约束可能只是拿来用,但是,呃,详细讲解的并不多, 我们正好延续啊,我 eda 流程的一个案例就是八位的计数器,讲一下持续约束啊,这本来也是一个简单的案例,我争取能讲明白啊。 那么持续约束他是什么呢?就是他不是代码逻辑啊,他是给 eda 工具下达硬性指令的啊,告诉你这个电路必须跑多快,我就让你就是换句话说,告诉他的速度啊,这就叫持续约束啊。那么 拿咱们这个八位计数器的案例讲解呢,就是如果代码告诉了你,我怎么去做的这个八位计数器啊,但是它只是说功能上我实现了八位的加计数,但是没有规定我什么时候做完。 而持续约束做的事情就是告诉你这个文件里面就告诉你啊,它和 filter, 就是 咱们在 e、 d a 的 这个 流程里不讲了过 filter 吗? filter 是 什么?布局布线,对吧?我们说把代码翻译成物理硬,呃,物理硬件,物理硬件呢?就是比如说 le 啊,或者是 le 里面的里头,比如说 l u t 啊,或者是寄存器啊,那么 我很多呀,我我我我,本来那个我的芯片里有很多呀,那么 filter 布局布线呢?比如说你不去规定,那么它就相对随意,我只要完成你功能就可以了呗,对吧? 然后呢,但是啊,如果你写了十句约束,那就不可以随意了,因为比如说我的持续约束文件里我会怎么样?我会要求一个时钟频率,比如说一百赫兹,呃,一百兆赫兹,那么一百兆赫兹, 你你你,我就要求你不拘不限,你要根据我这个频率走,那么一百兆赫兹,也就是一百乘以十的六次方在倒数啊,那么相当于多少呢?是十纳秒。那么再做一个加加一的这个逻辑路径, 就是,换句话说,你布局不限了,你就要小于十个那秒,如果你不在这个时间结束这件事情,我下一个技术就又来了,我下一个时钟又来了,对吧?那么就直接影响你的最后结果了。所以呢,他说了 什么叫持续约束?这个文件实质上是跟 e d a 工具里面的 filter 布局部件,他们之间是有合同的,不是你随意的排布,随意的连线, 所以没有。如果没有约束呢?那你说你不写这个东西,费尤特就可能为了省事啊,就是可能就是把逻辑上我实现这个逻辑就可以了,那我可能是乱放就会导致延迟过大, 有了约束呢?哎呀,费尤特就想,我必须在这个呃这个频率或者这个周期范围内必须完成,那么他就呃 就不会绕远路,也不会走太快,不是说光要远路,走太快也不行,所以要满足不要绕远路,也不要走快线来满足你的十种要求。 那么最典型的两个语句呢?就是 create clock, 就是 这个 clock name period, 就是 这是什么?十个什么,就是这个 十,是表示十个纳秒,跟什么连呢?跟 clock 连,而这个十个纳秒你是可以随意的,呃,就是设置的十个纳秒,就是食指上就是一百兆,比如说我们举的这个时钟频率就是一百兆赫兹,那么在这里你就会写十啊,这表示十个纳秒,嗯, 跟呃我的时钟信号相连,这是定义时钟,就是换句话说,我这合同里先说时钟啊,我总的总的时间线还要设一些 input, 还有 output, 那 么咱们先说 input delay 什么意思?你看延迟就是输入的延迟啊,那么这是另一个啊,常见的一个文件啊,的一个写输入的啊,写延迟,因为你看这个是两个大表, 他这个跟什么连呢?跟复位连什么意思呢?比如说通常情况下,我们在做硬件的时候,我们都会设置复位键,对吧?然后都是复位以后重新开始,呃,走这个程序,那么复位这个过程也不是说完全有可能是 理想情况下是一点不消耗时间的,但是有可能复位以后这个信号到达 f p、 j 还是有延迟的,那么在这里就是说,再说说,我定义告诉你,我会延迟两个那秒啊,那么你的十个那秒里头,你就要减去这个啊,我到延时的这个东西。 好,那么先总的说一下,就是说约束改变了,就是怎么改变呢?比如说下面这是一个第一个 q 啊,计算器里不记了一个 q 值吗?然后再计算是什么?再计算就是 q 加一,对吧,对于五十兆赫兹的啊,那么现在他从这到这就可以了。 那你说如果我频率改变了啊,我频率增大,咱们说别说改变,比如说我增大了, 增大了我的频率,实际上就是缩短周期,那么就是缩短时间,那你看一眼我增大频率的时候,那他俩就不能太远了,因为你的信号传输是要有有时间的,对吧?那么好,那么我,我这两个信号之间,比如说我再大一点,他俩就得再挨着近一点,为什么? 因为你在极高的频率下就要求他俩必须什么很快的传递信号,那么这两个寄存器之间,逻辑单元之间,你就尽可能的挨着,对吧?你才能完,呃, 保证你在这个呃时间段内完成信号的一个传输电子的一个运动。我觉得这个还是挺形象的,三百兆赫兹,比如说你就必须这么近了,那就你就需要近一点了。嗯, 这就是约束文件啊,跟 filter 之间的一个叫合同,你,你也对它有约束吗?为什么叫约束文件吗?对吧? 好,那么在这里啊, clock 啊,如果,那你说老师有没有可能不设置 clock? 没有, clock 说了,那么呃,工具,也不知道你是一百兆赫兹啊还是一兆赫兹啊,那么呃,工具软件就会以最低的优先级处理啊,那么 那你如果不去设置的话,那,那那,那八位的计数器可能就跑不起来。还有一个呢,叫定义时,呃,定义持续界面。 呃,界限什么意思呢?它就约束它定义了一个 set up 和一个 hold 的 边界,那么之前的 e, d, a 的 这个流程好长的,那个四十五分钟的那个视频里我讲了一下。呃, set up 和 hold up 什么意思呢? 一会我也会说一下。那么只有在这个界限内,这个信号才是可以生存的,在这个界限外,这个信号就死亡了,就不能用了啊。先总的说,约束是设计的意志, vlog 只决定了功能,而 sdc 的 一个时间约束文件决定了芯片的功能, 当你写下这个 clock 就是 create clock 的 时候,你就告诉了芯片,这是我的节奏,你要在我的这个节奏里,或者是物件,呃呃,世界物理世界里精准的实现它。 这总的说一下啊,总的说一下,那咱们就详细的拿一个还是刚刚咱们举的八位计数器的这个约束文件,说一下每一句话的意思,因为之前只只只只给大家看了两条,对吧? 那好,那么这个约束文件主要包括四块,一个是你要定义系统的主时钟,换句话就是刚才我说的啊,你到底要在一个什么时间段内啊?完成一个电子的 一个一个,一个一个,换句话信号的一个传递,那么比如说在这里我们要看的懂,那么在这里是这个,这个十是表示十纳秒, 因为我要定义的时钟啊主呃主时钟呢是一百兆赫兹,那你就倒数呗,倒数,然后就相当于十纳秒,那么在这块就是十纳秒,他连接到了时钟啊信号, 这是定义系统的主时钟。接下来一句叫自动计算时钟的不确定性,呃,又称之为抖动和偏斜,这个我们放在最后补充说一下这个的目的啊, 重点说一下约束,一个是主时钟,一个是约束,呃,约束输入引脚的延迟和约束输出引脚的延迟,就是我们的信号,不是说你连上, 呃,这个信号就从头到尾没有,那是理想情况下啊。好,主时间轴我们已经确定了,那么我们刚才其实已经呃,给大家举了一个例子,那么比如说这个 你看啊,这是输入的输入信号的延迟时,你看啊,他是什么呢?最大在两个,咱们说单位是两个,那秒 什么意思呢?通常情况下,我一个 fga 的 板子,我一摁复位,进入了就就就复位了吗?信号就从进入到一个初始状态,但这个过程是需要时间的, 那么 max 两个大,呃,两个大秒呢?就是说什么意思呢?简单直白啊,因为副微信号在进入 fga 之前呢,已经在外面的 pcb 走线耽误了两个大秒,换句话说,我的总 时间是十个大秒,那你在这里我最大可能耽误了两个大秒,那么你就得重新计算了,我这个步线怎么走,对吧?最大也有可能最小是没有的哈,这是输入的延迟。输出的延迟是什么呢? 输出的延时,你说,哎,老师,你你,直接就,你你你,你把这个一计算出来就出来吧,也不是这样子的,我们要求什么呢?我们要求计数器的输出带再到达外部器件, 就是你要求需要一点五个那秒的稳定时间,也就不,不是说你来了我就立刻走,因为下一个前一个信号是需要一定的。呃,稳定时间的,稳定周期的,你过早的过去了,你会把前面的旧值冲掉。 所以呢,你要在这里设定一个,就是输出的时候要到达外部期间的时候要有一个稳定时间。 稳定时间,那么在这里头啊,我们设置了一个一点五纳秒啊,就是不能过快,当然当然也不能过慢。嗯,那么这个就是什么呢?就是 filter, 看到这个 o, 那 我就会把 q 的 一个相关的 le 尽量放在最近的 l 引角的地方 啊这是,这也没跟你说吗?这,这一套语言 s d c 是 给 filter 看的啊,啊,我,我前面输入的引脚的延时最大要求多少?你不能超过这个,超过这个我们就,呃,没有信号就就会出现混乱了。 还有输出我也会涉及到什么,输出也也是有,也是有延迟的啊,输出也是有延迟的啊,需要稳定信号都告诉 filter, 那 么他就要根据这个换句话说约束条件,我去布局我的啊,逻辑单元,逻辑单元, 好,这又是写了一下,为什么要写 sdc, 他 就是合同机制啊,他叫 contract future 是 一个懒惰且高效的员工啊,如果你不告诉他的周主持之中,他就可能按照十兆,比如说你原来是一百兆,你不告诉我一百兆,我就可能按十兆去布局, 那么 sdc 呢?你,你告诉他一百兆了,那他就要拼命的去根据这个一百兆的时间去布局。嗯,好,那么物理对齐就写到就是,为什么要写 sdc, 还有一个物理对齐就是什么呢?引脚约束,无论是输入还是输出,它决定了你的输入引脚 和输出引脚就是这些他们之间的位置啊,因为 sdc 决定告诉你了啊,输入啊, 呃,之间的有一个输入过来有个延迟,然后输出呢?还有一个稳定时间,那么这些所有的时间加一块就决定了你在 future 布局不限的时候,你不是很随意,不能随意的进行。好, 那么所以说呢啊,哎,代码 very big very log 的 代码只是管逻辑功能,而真正时 管就是管这个代码的生死的是 s d c, s d c 啊,所以呢, s d c 是 实现持续收敛的第一步,没有约束的 f、 p、 g a 呢?就像没有红绿灯的交通网,那么车辆呢? 换句话数据呢?再快最终也可能打就就造成了追尾啊,等一些事故。好,那么呃,咱们再详细说一下,那你说这个,哎,那个两个毫秒和一点五个毫秒啊?这个从哪来的呢?咱们再稍微或者是这个定义是什么, 咱们再详细的说一下。就具体的这个时间,那么 sdc 啊,频率这块不用说了,你就就规定,比如说原始周期一百兆,那他总的时长就是我要在十个纳秒,这就是这个蓝色表示十个纳秒, 你要把我这件事情完成,对吧?那么好,咱们不说这输入一个量吗?比如说复位啊,那么他刚才写的一个是最大的一个复位信号的延迟是两个,那你就要消耗两个纳秒, 还有一个是这中间还有一个叫时间不确定,时间不确定啊,假设时间不确定,然后 我们这么减完没有其他的话,那么你看内部剩余空间,我就就十减去二,再减去零点零五,是不是啊?内部消耗内部剩余空间的时间就是七点九五,就这么了得来的。 那么我们要强调两个概念,再详细的说一下,叫建立时间边界,它是什么意思呢?它就是关门前必须赶到, 就是 s、 d、 c 啊,定义了我们门什么时候关,保持时间边界呢?就是告诉你关门后不能马上走, sdc 需要你再待多久,需要你再待多久,这就是我们之前其实在啊流程中讲的在后边的持续分析啊,持续分析中两个关键的量,这俩量是博弈的啊,是博弈的,你 来的太晚也不行,走的太快也不行啊,这是一个博弈的。那么如果从一个动画的一个 一个一个,这个是相当于给了一个动态的啊。要比如说时钟周期固定以后,时钟周周期固定以后,那不就是总时长是固定的吗?那么你的输入如果延迟太多的话,你看比如说我输入耗外部耗时很多,那么就没有剩余了,那么这个信号就就就宣判死亡了,宣判死亡了。嗯, 但我这时钟周期可以改啊,时钟周期可以改啊,如果你这时钟周期比较长啊,我可以,就是换句话说,我也可以很长时间完成这件事情,那你稍微延迟一点可能也没有事。你要比如说我这个时钟周期,你看他有很大延时了, 这是八个那秒还没有完事,就还可以色变,还可以色变,但是对于极短的极短的时钟周期,比如说这五个那秒的时候,你看这这他的生存空间就很少了,很少了啊, 就是稍微你这边有延时输入,延时的话,我的我的我的我的就判,你要状态判决就淡死了,办状态判决就淡死了,对吧?所以, 呃呃。时间约束文件的四大指令,第一个确定主战场,也就是确定系统的主时钟啊,规定了时钟轴的一个圆点和中点啊,就是换句话,总时长,总时长啊,你要在这个时长内电子要完成,在这个时间内完成一生 啊,这这主持中毫无疑问,然后就是建立时间,就 input 建立时间,那么在这里头 max, 呃,判断机制就是什么意思呢?就是门前赛跑,它简单的说就叫门前,你必须在这个门关之前必须怎么样进来?工具会 认为电子从起点出发,时间啊,已经断了,就比如说你总是尝试还在,咱们还按一百兆走啊,那么就是相当于十个纳秒,你这个如果最大是两个纳秒,就认为你不是从零起点的,你是从两个纳秒才开始起点的,所如果上下路径太长, 电子就会怎么样?在十纳秒关闭门之前还没进场,那绝对的这个就叫死亡判决,就 set up uh violation 啊 violation, 所以 就是 set input delay max, 就 叫建立什么建立时间,它建立就是你必须在这个门前赛跑,必须在这个门关之前必须进来。还有一个是这是 你不能太慢,你得进来。还有一个你不能走的太急,叫 set up output delay。 他的判断机制呢?啊,比如说如果你设了一个啊零点呃零点一, 那么工具就告诉你,你必须在啊,就是负的零点一那秒,你必须在时钟边缘后继续维持, 如果新数据来的太快,你要你你不去维持的话,新数据跨一下来了,旧数据就被冲走了,那么你后边的逻辑就全全乱掉了。也是一个叫 hold violation 啊,这就是叫呃 set in, 呃呃 input delay 是 建立时间,还有 set output delay 啊,这是什么就是什么保持时间,你 不能走的太慢,但是你也不能走的太急,那么中间也要涉及到一个量,叫呃 di 呃 device clock and uncertainty, 就 叫生存安全系数,就是很多事 尤其到硬件以后就不是理想情况下都有一些不确定的,那么是什么呢?比如说他考虑这个时钟有可能有抖动 jitter, 那 么他在十纳秒内,他在十纳秒的终点处,人为的他就往什么 往回推了几十皮秒就是安全吧,给给咱们自己都有个安全系数,就叫未雨绸缪的死亡缓冲区。就是你别呃,满打满算十个纳秒就往前,往前来一点,确保在极差的环境下,电路也不崩溃啊,我相信这个大家是可以理解的, 那么从时间轴上没有平庸,只有生和死,什么意思呢? stc 文件不是简单的配置文件,它是一张严密的物理时间网络, 它通过,比如说咱们举例子,是八位计数器的一个案例,那么你就不再是一个代码的一个搬运工,而是一个能够掌握物理微观世界的一个架构的一个一个状态啊。那么在这里再补充说一嘴什么呢? 因为啊,既然我相信这个粉丝问到了持续分析,那么呃,还要有几个量,我就再拓展一下,我记得我在 啊,其实你看啊,这是咱们之前的,呃,有一个量啊,我记得我,我搜了一下 啊,一个是始终偏斜,一个是始终偏斜,就刚才不有一个自动吗?设置始终偏斜,那么这个是干什么的呢?啊?补充,再说一下,其实我在 e、 d、 a 的 流程中我说了,但是那块可能没有重点说,我相信在这一块你会了解, 那么比如说八位计数器中,时钟信号应该同时到达所有的触发器,实际上呢,呃,就是它是长短不一的,会导致歪斜。什么叫歪斜?一个正向的,一个负向的 正向歪斜呢?就是啊,目的端时钟晚到,就是就是相当于变相的给数据更多的跑路时间,也就是说,那么就是正向偏斜,就是对 set up, 就是 建立时间有利,但是极易引发后端的 hold, 就是 那个后端的那个 hold 的 追尾,这就叫正向偏斜。还有一种副向偏斜呢,就是什么呢?它对 set up 是 极其致命的, 但是他缩短了有效时间周期,就是什么意思呢?又有个自动调整的吗?就是你还是这个意思, set up 和 hold up 他 们是一个博弈的过程,博弈的过程不能太快, 也不能太慢,也不能太慢。嗯,好。再说的一个就是啊,我我我搜到了这个量啊,作为补充啊,作为补充, 比如说还是这个八位的计数器,那么食指上如果你接下来看到一些芯片的一些参数的时候,比如说遇到这几个量,我相信啊,你要知道它是干什么的, 那么比如说啊,还是塞克隆四的一些物理参数的基准会遇到几个参数呢? t c o t logic t nite, t s u t h, 它分别代表什么呢啊?分别一个是代表时钟传输, 呃,以时钟传出,呃,输,输出的一个延迟,就是时钟的跳变到数据离开的一个计算器的时间。 嗯,这是呃,就是接下来细话啊,你要知道这个量,但是我也没有细讲,但是就是说如果你遇到芯片的具体参数了,咱们也知道 set up, hold up 啊,还有一些正向偏斜,呃,负向偏斜,这些都是干什么的?但是如果遇到再细节的,比如说这 tco 啊,叫时钟输出延迟,还有 tlo 这个就是比如说还是拿八位计数器这个练,呃,这计数器,这这个案例来说,那么就是八位的进位练 逻辑延迟啊,就是比较细了啊,它们都有延迟时间,还有 t nate 布局布线,也就金属线上传输的一个消耗啊,金属线上,对吧?到了物理硬件就不是所有的情况下都是零秒的,对吧? 还有 t s u, 就是, 这就是什么建立时间要求,这个就是刚才我们说的叫数据必须提前到达窗口, t h 就是 保持后,对吧?啊? ph 就是 刚才我们强调的叫保持时间要求,就是时间啊,时钟后数据必须锁死的窗口啊,这个两个,后两个我们是前端已经或者一直在强调的,那么这两个,这几个量,其他几个量呢?大家知道一下。好,这就是啊持续约束。

28一路彤行 07:23查看AI文稿AI文稿

07:23查看AI文稿AI文稿从精元产能、 fpga 测试瓶颈,到 ai 算力吞金,带你拆解内存涨价的技术加商业双重逻辑。上周给测试版换 ddr 三缓存,采购同事甩过来的报价单,差点让我把 fpga 测试脚本删了。才半个月, 单颗 ddr 三颗粒涨了百分之二十二。一开始我以为又是供应链老套路,无非是某个港口堵了,某条生产线炸了这种传统异能。结果查了三天,经原厂价动率、原厂测试量率报告、 ai 厂商的抢单数据,才发现这次涨价的水 比调 a 叉 a 总线持续约束还深。普通用户看到的是电商页面上 ex 九九 u x 九九的涨价标签,我们工程师能看到的是 清原厂的高端设备被 ai 订单锁死,滴滴二五测试量率卡在瓶颈上动不了,甚至连测试用的 a t e 机都被抢成了香饽饽。今天我们扒一扒这次内存涨价的技术加商业双重逻辑。第一部分,从芯片出生看,能真的不是想加就能加。 很多人说内存厂商故意减产抬价,明为了 it。 二四分之是给消费及电脑、手机用的平民量,是高端产能被从根上锁死了。 一不是没能源,是好能源,都去给 ai 当口粮了。内存也分三六九等, d d 二四分之三是给消费级电脑、手机用的平民粮 lp d d 二五 d d 二五服务器级是给 ai 服务器位的特供粮。之前全球内存的分配大概是七比三, 七成给消费级,三成给服务器级。但今年 ai 大 模型爆发后,这个比例直接反过来了,八到十六根 ddr 五内存,而且必须是带 ecc 纠错的工业级颗粒,这种颗粒的制造工艺要求比消费级高三个等级, 十纳米以下高端制成产物被微软 openai 国内大厂的 ai 内存订单直接包年。消费级 ddr 三斜杠四只能用剩下的老旧生产线。我查了三星 q 二的产报告, ddr 五服务器级颗粒的架动力是百分之九十八,而 ddr 三消费级的架动力只有百分之六十二。 不是不想开,是能生产高端颗粒的设备根本腾不出手做低端产品。二、测试环节的隐形瓶颈比能源不足更致命。内存不是从晶源上切下来就能卖的,光是颗粒测试就要过三轮高考。 功能测试、持续测试、稳定性测试,每一步都离不开 fga 验证,但现在连出题的老师都被抢光了。高端 ate 测试机原本一半用来测内存,一半用来测 ai 芯片,今年 ai 芯片厂商直接包下了全球百分之七十的高端 ate 机 内存厂商拿不到测试产能,生产出来的颗粒只能堆在仓库里等测试。量率, d d 二五的信号频率是 d d 二四的两倍,测试时的抖动物理误差会导致量率比 d d 二四低。百分之十五 相当于每生产一百颗, d d 二五就要废掉十五颗。我上周测一片 d d 二五样品光调整 d q 信号的持续就花了两天, 量率只有百分之八十三,比去年同期低了十二个点。内存类型,单颗测试时长量率测试设备需求 d d 二四四十 s 百分之九十七。普通 a t e 机 d d 二五一百二十 s 百分之八十二高端 a t e 机 工程师旁就这量率,相当于你写了一百行 value 代码,十八行会报语法错误,而且测试时长翻三倍,等于原本一天能测一千颗,现在只能测三百颗, 成本不涨价才怪。举个通俗的例子,你烤了一百个面包,但只有八十五个能通过质检,剩下的十五个直接扔掉,成本能不涨吗?第二部分,需求端的畸形抢单比产能约束更疯狂。如果说产能是硬约束, 那需求端的抢单就是火上浇油,而且是 ai 带头放火,消费端跟着起哄。一、 ai 厂商的抢单暗战, 用钱砸出内存涨价潮。国内某 ai 创业公司的硬件工程师朋友跟我说,他们现在拿滴滴二五颗粒的优先级,还不如给大厂做配套的小厂商,人家一张订单就是十万根,每根加五十块钱现金,我们这种一万根的订单人家根本不想理。更夸张的是所产能, 有些 ai 厂商直接和三星、海力士签了产能锁定协议,提前预付百分之三十的货款,把未来六个月的滴滴二五产能直接包圆,不管市场行情怎么变,你都得先给我供货。这就导致服务器及内存的价格已经翻了两倍,还拿不到现货, 消费级内存只能跟着水涨船高。二、消费端的恐慌性备货成了涨价的帮凶。当电商页面出现库存不足,即将涨价的标签时,用户的第一反应是赶紧囤,经销商的第一反应也是赶紧屯。原本消费级内存的库存周转周期是一个月, 现在经销商把库存周期拉到了三个月,相当于市场上平冲少了两个月的货量。我问了深圳华强北的朋友, 现在经销商手里的 ddr 三颗粒能卖到比原厂报价高百分之十五的价格,而且还不愁卖。 pc 厂商更狠,联想惠普今年 q 三的内存备货量比实际需求多了百分之四十,就是怕后面涨价涨的更凶。这种越涨越囤、越囤越涨的恶性循环,直接把消费级内存的价格推上了天。第三部分,政策与资本的无形推手,把涨价玩成了游戏。 如果说能和需求是明面上的原因,那政策和资本就是暗地里的推手。这波操作比我们做持续仿真实的延迟注入还稳局。 一、芯片出口管制,逼着国内厂商抢货。美国对 ai 芯片的管制,直接导致国内 ai 厂商疯狂囤内存,原本可以通过服务器芯片加内存的配套采购拿到优惠价格,现在只能单独高价扫货。更坑的是供应链重构成本。三星为了规避管制, 把部分 ddr 能源从韩国转移到越南,光设备调试人员培训就花了两个亿,也只是注入期,这部分成本直接转嫁到了产品价格上,相当于每根 ddr 三颗粒涨了五块钱。二、资本炒作, 从期货到现货的连环套。我查了内存期货合约的价格,今年以来, ddr 五期货价格涨了百分之三十五,而现货价格只涨了百分之二十, 这说明什么?资本提前半年就开始布局,先炒高期货价格,再通过媒体放风要涨价,最后在现货市场收割一波。这就像我们做 fgp 设计时的持续违规,你以为是信号延时导致的问题,其实是资本提前给你加了延迟, 等你发现的时候已经来不及调整。结尾给普通用户和工程师的几句实在话 给行业人。这次涨价不是短期波动,是内存行业的转折点。未来三年,内力初期, bdr 服务器级内存的需求会持续增长,消费级内存会逐渐进入高成本常态化阶段。 作为工程师,我们能做的是优化设计方案,用更少的内存实现更多的功能。最后说一句,内存涨价的本质和我们做 f p g a 设计一样,都是资源、能源需求的博弈,只不过这次的棋盘是整个全球半导体产业链。

10至疯狂的芯 08:45查看AI文稿AI文稿

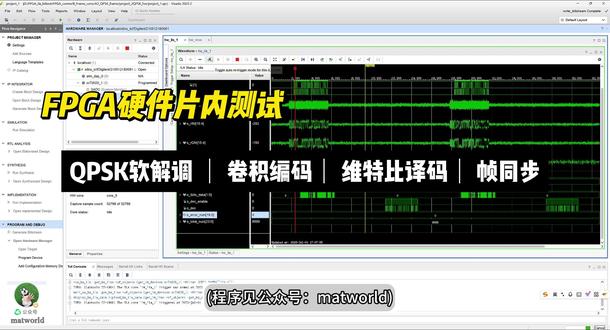

08:45查看AI文稿AI文稿朋友们大家好,我是五 s c 编程,今天我们介绍基于 f p e a 的 q b s k 调制卵解条,然后是转机编码,维特比异码以及帧同步系统 做一个硬件啊操作演示。首先我们打开工程,打开之后的话可以看到有这一些模块,我们依次介绍一下。首先这是测试的数据源,我们产生一帧一帧的随机数据, 然后这个是 vio, 用于设置 s n r, 我 们在硬件调试的时候,可以通过这个 ip 盒实时的调成信道的信噪比,然后这是 qbsk 顶层文件,它包括二幺七转机编码调制信道解调节调内部的话有针同步, 然后针筒布置后的数据进行维特比一码,然后再雾码统计,然后这个是 i o e 文件,用于在线啊显示各个接口的波形数据。下面我们对该系统进行啊测试片内测试,首先进行综合布局布线, hmm hmm hmm do you i don't know you i'm i'm not i'm not。 好,然后我们再进行啊产生笔头文件,点这个 好,然后我们再连接开发板,点击这一个自动连接 好下载程序, 然后,嗯,抽取下来之后,它的波形应该是这么一个形状啊,我们首先设置 s n r, 如果这个地方没有 s n r 的 话,我们点这个加,然后讲 s n r 加入这个就是 v i o 控制的信道比设置变量啊,比如我们一开始设置的二十 db, 然后在这个 trigger 里面,我们将选择这个变量,点这个加号,然后选择这个变量设置为一,这样的话我们每次刷数据的时候可以刷到当前数据帧,然后点这个采集数据, 好,然后我们再将几个波形文件设置为有符号时间制,然后再设置为波形模式, 可以看到二十 db 的 时候,它的叫声是非常小的。然后我们介绍一下各个波形的含义。首先这讯噪比,这是发射数据, 转接编码之后变成两路数据,然后这是 qps, 可以 调制信号啊,这里多处的一段是它的导频部分,也就是我们家的针头,然后这个的话是相关风,我们放来看一下, 它会明显大于啊其余部分的数据,然后根据这个相关风使能我们产生啊针头以及数据部分,然后这个的话是雾霾统计 啊,如果下载过程中它出现了雾码,可能是下载初始的时候出现了问题啊,比如说二十 db 的 时候,它现在有七十七个雾码,理论上是没有雾码,对吧?如果出现这种情况的话,我们重新下载一下就可以了, 棚没有雾霾,然后我们这里可以降低信道比,比如说十 d b, 好, 十 d b 出现零星雾霾,我们再刷一下, 好,再刷一个五 d b 好, 出现零星雾霾, 按下设置十二 db, 嗯, 好。然后我们再设置啊,比如说八 db, 好, 然后我们可以再设置小一点,比如说三 db, 这个时候照射会非常大。 好,三 db 的 时候出现一些零星雾霾, 好,大概这么一个效果啊,演示完毕。

16:39查看AI文稿AI文稿

16:39查看AI文稿AI文稿啊,朋友们大家好,我是五 s 边能,今天我们介绍一下基于 f p g 的 f s k 调制解调加扩频解调扩频解扩通信系统 啊硬件篇内测试。首先我们打开工程,打开之后的话,我们简单看一下整个系统的结构啊这个是硬件啊测试时的顶层文件,这个文件的话需要跟硬件进行接口约束啊,具体约束的方法的话在薄荷中有介绍,然后这是分频器, 然后这是信号源模拟产生随机的数据,然后这个是 vio, 在 测试的时候我们通过 vio 可以 在线啊修改信道模型的信噪比, 也就是这个模块,然后这个的话是 fsk 啊调制解调底层文件,它包括扩频调制、信道解调节、控码检测,然后在啊解调里面我们增加的一个模块叫 啊定时点提取,我们通过定时点提取之后,可以对 fsk 解条之后的啊数据包络进行采纳判决,从而得到标准的二进值数据, 再对二进数据进行啊解扩。那么在解扩过程中,我们这里增加了一个模块叫啊扩平码啊同步 扩比维码同步啊,基本原理的话跟啊针同步类似,通过一个扩平码的一个相关风的检测,根据相关风的啊风直位置来捕获到扩平的啊解扩,是啊解解扩七十时刻,然后再进行啊扩平结构的处理, 那么这种方法的话可以有效呃抑制噪音带来的干扰,然后这个的话是 lv, 这个 lv 的 话我们将啊整个系统中一些关节信号记录到 lv, 那 么在硬件调试的时候就可以进行实施的判决, 下面我们对该系统进行演示啊,首先对整个系统进行综合布局布线,那这里的话我们点这个按钮,点这个 好,这里稍微耐心等待一下 好,然后再要产生 beat 文件, 然后我们再打开卡 板, 然后下载程序, 好,下载完之后的话可以看到有这些啊接口,然后我们啊做一下设置,在触发里面我们选择这个 m, s, g, n, 这样的话我们就可以保证每次刷到的数据是帧头位置 啊,改为 e, 然后在这个触发 setting 里面将这个时间设置为两千, 好,点击刷新一下, 可以看到有这些波形,那么我们简单介绍一下这些波形的含义 啊。首先第一个的话信号比,默认的信号比是十五 db, 然后这个的话使能信号, 然后这个的话是原始的数据源,然后这个的话是扩屏之后的数据源,我们可以放来看一下啊,一个符号,我们通过啊多个扩屏码进行扩屏, 然后这个的话是 fsk 调制啊,可以看到对高电频我们采用一个高频率的再拨 啊,如果第一次使用的时候它下载完的话啊可能是这种形状的波形,如果是这种形状波形的话,我们只要打开, 首先设置为有符号式帧制,然后再在这个地方设置为波形设置, 然后将这个高度,比如说设置为一百,然后这个刻度的话可以根据幅度大小进行啊设置,那这里的话它这个数值范围一般在正负一千左右,那么为了显示完整,我们可以设置为一千五,只要比这个波形的最大值和最小值稍微大一点就可以了,然后这里点击为后的 啊,这样就看到波形了,然后这个的话是通过信号之后的 f s 可以 调制信号,可以看到有招生干扰,然后接收端解调低通滤波, 然后这是相关风,那么根据根据这个相关风,然后再进行第四点提取,然后根据第四点提取,我们对这个 fsk 解调后的数据进行啊裁案判决这个信这个数据的话就是前面扩平之后的数据,然后再进行解扩, 最后我们对解库后的数据进行雾码统计,这里的话我们统计的是一万个零到九千九百九十九一万个,然后雾码是零,然后在这个地方的话我们啊改一个,比如说是负五 db 啊,可以看到负五 db 的 时候,它这里雾码依旧是零啊,这个的话也基本符合啊扩频的性能,这里我们仔细可以对比一下 啊,原始库名后的数据的话,这里可以看到明显已经有了很多错误,但是通过库名之后的话,我们依旧可以恢复出原始的 r n g 数据。 好,大概就这么一个效果,演示完毕,谢谢大家 啊!这里做一下加入负五 db 噪声之后,由于噪声非常大,所以这个地方刻度会要改一下,刚才我们设置的是负一千到一千,那这里可以改为负两千到两千啊,这样的话可以看到加入噪声之后的数据, 几乎啊是无法看到原始的 fsk 信号的,待通过解过后,我们可以恢复出 r 整数数据。好,演示完毕,谢谢大家。

02:34查看AI文稿AI文稿

02:34查看AI文稿AI文稿朋友们大家好,我是我爱 c 编程,今天我们介绍基于 f、 p、 g、 a 的 d、 c、 t 变换实现,这个版本是在 cortis 平台下实现的,我们通过 cortis 十八点零打开这个程序,然后我们进行演示,首先点击这个三角形, 然后点击 tools, 点击 run simulation, 这个时候 cortus 会自动调用 model sim 仿真软件进行仿真, 然后我们点击这个放大镜,可以看到它的数据,然后我们将数据已有符号时进至进行显示, 其中前八个是我们的测试符号,我们用不同颜色表示,后面八个是 d c t 变换的输出。为了验证其正确性,我们写了一个小的 matlab 程序, matlab 程序的运行结果是这个,这里我们可以对比一下。我们看到它的数量级是基本一致的, 但是由于 fpga 里面运算过程中存在大量的未宽截取以及量化等过程,它会带来一定的误差,但它基本上能保证在相同数量级下的一个数字输出结果。 这里注意一下。在 cortis 中调用 model sim, 我 们这里需要做这么一个设置, 首先我这里是 model sim o terra 版本,它这里有很多版本,所以在实际用的时候得选择一下您的版本是 modison 还是 model sim o terra 版本,这个需要注意一下,否则可能会仿真报错。 以上就是整个系统的演示过程。

15:48查看AI文稿AI文稿

15:48查看AI文稿AI文稿agmfpga 新建工程编辑下载 硬件连接完毕以后, 然后通过两个软件进行操作,第一个软件是这个,呃, cortas, 我 用的是 cortas 二,然后十三点一的版本, 然后第二个软件就是 super, 这个是 agm 官方出的,必须得用它和 protos 才能完成这个综合编异部布局布线,然后下载这些。 然后第一步从这个创建工程开始讲,首先创建一个这个工程工程文件夹,里边有两个子文件夹,一个是 agm, 一个是 auto, 然后第二步就是说打开 super, 点 project, 然后 new project 创建新工程嘛,然后这个位置选择咱们这个目录,对吧? 因为是用 suprise 嘛,所以说我把这个目录放在这个 a g m 这个指纹夹下,然后工程名字随便,然后点 save, 然后这就创建完了,并且这个工程创建完了,它就帮你打开了。 然后接下来的操作就是回到这个 cortas 这个软件里,然后在这个 cortas 软件里边也是点击这个 file 文件,然后 new, 然后 new cortas 二 project, 创建 cortas 二工程, 然后这个位置也是咱们创建之前创建的那个文件夹,我是放到了桌面上, 然后选这个 auto, 这个文件夹刚才选的是 agm, 现在选这个 auto, 这步非常关键,不能放一起,必须得分开放 auto, 然后选择文件夹就行了。 然后第二个就是咱们工程名字,对吧?我这就是一个简单的事例,就写了个让它产生这个 pwm 放波的一个程序,然后点击 next, 然后这个位置呃, add file, 这个其实就是说如果咱们要是有写写好的这个点微就是模块文件,咱们可以在这个创建工程的时候可以直接添加进去,我这有一个县城呢,之前写好的 桌面放到这个 auto 文件夹里了,这有个 pwm, 点 v, 然后双击它,然后点右边这个 id, 添加进来之后,然后点这个 next, 然后这个位置是选这个硬件型号,咱们用的是塞克隆四 e, 然后右边选择封装封装盒这些参数, 然后这就快速找到了,这个用啊,用这个 a g 幺零 k 来替代这个奥泰利亚他家这个 ep 四 c e 幺零 f 幺七 c 八,核心电压是一点二伏的啊,有十千个,一万个单元,然后 next, 然后这一步是调试 工具设置吗? e d a 工具设置,然后这个这个里边选择这个 mode, 然后点 next, 出现这个界面,咱们这个工程就创建完了,然后直接点 finish, 然后创建完了之后,在窗口的左上角会有这个咱们选的芯片的型号,然后点这个 files, 这是它文件结构,因为咱们之前添加了一个点微,它就会出现在这,然后咱们双击这个文件,右边就可以进行这个程序编写。 啊,它这个程序我我之前这个程序写的很简单,很简单,就是它就是一个记这个使用周期,然后通过这个啊 i o 口,就咱们那个芯片的引角输出,引角给用户的那个 i o 让它进行翻转, 对吧?上边这个就是说呃模块的这些输入输出这一个定义,前面是输入输出,然后右边是这个信号名称,右边什么 clkrestn, 这是给呃咱们那个晶振这个复位信号, 然后 out put, 这个是 pwm, out 这个这个信号的引脚,对吧?然后下边有两个寄存器,分别给了两个值,这上面这个 preload 的 cnt, 这就是,呃,周期, 就是说我跑,我跑五百个周期,然后就执行一个什么操作,下边这也是一样,这是这是调帐篷笔的, 然后底下这个 always 块,这里边就是具体的这个程序的逻辑,对吧?就说记记这个五百个时钟周期这个数可以自己改 记五百个这个使用周期,然后对这个引脚进行操作,至高或者至低,然后下边也是跟这个帐篷比的这个进行比较,然后最后输出,输出咱们这个想要的这个一个信号程序很简单,就这些东西, 然后咱们把这个程序写完了之后点保存,然后在右边,因为这一个很简单的程序,它没分文件写,我直接就把这个文件设置成顶层文件, set our top live, 哎,这样这样就可以设置完了。然后咱们再回到 super, 然后在 super 里边点这个工具 tos, 然后点 prepare, 然后在这个 prepare 的 第一个栏里边选择咱们这个工程文件夹的路径, 它这个操作比较繁琐,就是这个两个软件之间要来回切,但是记住这几个关键步骤就不会出问题。第一个路径选择咱们那个 corto 这个子文件夹,然后选中之后, 下一个是他的这个时间约束,就是持续约束的这个文件。 sdc 这个文件因为咱们没做持续约束,所以说先不用选下边的是,呃,这个是咱们芯片的这个型号,我用的是 ag 幺零 kf 二五六,用来替代那个飓风四嘛,对吧?下边是这个点 ve 文件, 这点 ve 文件呢?正常的话就是说咱们新建工程的话,得需要手动新建个文文本档,然后把这个程序把这个 ve 文件这个程序写进去,然后保存放到对应的目录就行了。然后我这有一个写好的,给大家看一下它具体是什么什么样子。 open, 然后 auto 点 v e, 这个点 v e 文件那个格式也很简单, 前面是信号名称,对吧? clk 跟刚才咱们那个 model 里边那个信号名都是对应的,一对应的,前面是信号名, 后边是咱们这个引角名,就是说这一句每一行只能写一个信号,对,一个引角,这一句的意思就是说把把这个 e 一 这个引角,因为它是 f, 它是那个呃, bga 的, bga 的 那种封装嘛,它那个都是分 a、 b、 c、 d、 e 的, 然后它这个是 e 的 引角, 把这个引角连到这个 clk 这个信号上,这个信号就直接连接这个芯片外边的晶振,就咱们给他这个 hse 信号。然后第二句也是把这个 d 连到这个复位 复位信号上,把这个 a 九连接到咱们要的那个输出信号,那个引脚 pwm alt, 就 这个意思。然后咱们继续下一步说到这个 ve 文件吧,咱们就在这添加咱们之前的 ve, 你 看它很繁琐,就是需要这样来回的切换,对吧?然后选中,把这几步全部都设置完毕之后,然后点下边的 run, 然后当右边出现这个 d o, n e 当当了之后,然后这就说明它跑完了,这个程序已经执行完了,并且没有出错。然后咱们再回到这个 cortas, 在 cortas 里边点屏幕上面这个 tools 工具,然后 tcl scripts 就是 tcl 脚本。 因为咱们之前在呃这个 super 里边不是 pre prepare 一下了吗?它 prepare 执行的过程就会在这个下边生成这个 prepare 这个脚本,然后咱们直接执行这个脚本,选中这个 prepare, 点 tcl 点 run, 然后它就会出现一个这样的界面, 然后现在他就进行这个综合翻译这些操作了。但是咱们其实只要他一个导出一个这个网表,网表的这个一个文件,然后咱们用这个网表文件在 super 里边进行真正的这个呃,布线,布布局,布线这些操作, 这已经跑完了,对吧?已经全部都完事了。然后咱们再回到这个 super 里, 在这个 suprise 里边点击这个 migrate tos migrate, 然后也是在第二个这个栏里边选择咱们这个工程的这个 ootera 这个子文件夹, 然后第二个选择这个呃,咱们这个工程的名字,第三个就就是这个芯片型号,然后第四个是这个 ve 文件, 是吧?也是在这个 altair 下边 pwm 点 v e, 然后下边这些不用动就用它这个 comptable, 还有这些都不要选,就用它默认就就可以了。然后直接点 next, 然后它会跳出一个这样的界面,就是说这个界面它会告诉你,你看它说接下来怎么怎么操作,然后对吧?回到这个啊 cortas 进行运行这个脚本,其实这些咱们都不都是已经操作完了吗?这就不用管它,看到这个界面就可以了,然后左边的界面是这样的,然后咱们继续点下一步 next, 对 吧?然后看到一个这样的界面,其实这个界面就是咱们工具里的这个 compi, 就是 点 finish, 然后它这个时候右边就会开始跑了, 从现在执行的这个工作才是真正意义上的布局和布线。咱们之前 qq 里边那个咱们用不了,必须得通过这个 super r 进行转换,他转换的其实关键就是这一步,这一步结束了之后生成的文件就是咱们要的这个烧录文件、比特流文件, 然后在这个信息里边,咱们可以看咱们使用了,比如说时钟的这些这些关键信息,然后还有像什么资源占用,对吧?逻辑单元数,然后这个呃,比如说像这个他这个, 这个是他这个呃,端口引角,对吧?用的这个信号端口引角,诸如此类吧,对吧? 比如说用了这个十五个单元,相当于占用很低,因为程序很简单嘛。然后当底下看见这个蓝色的字,还有这个当,那就说明这个比特流文件已经生成完了,然后生成完这个比特流之后还是在这个软件里边进行操作, 咱们之前那个 migrate 已经跳到这一步这个界面了,对吧?直接点 ok 关掉就行了。然后点这个 tos, 点这个 program, program 里边选这个,咱们用这个下载器,这个 fpga, 千万记住一定要用这个官方出的这个 usb blaster, 也就是这个硬件 就是闪灯的这个,并且它这个灯现在这个慢闪,就代表这个 blaster, 在这一步一定要选这个 blaster, 不 能选这个 type link, 就是 c m s s type 这个 type link, type link 是 不能用的,必须得用这个 blaster, 选这个 blaster 之后,底下这些都不用动,然后点这个 id, 如果这个位置能读到这个 id 号,对吧?他不是全是零,或者是不是报错,那就说明咱们硬件连接是没问题的。然后这个位位置就添咱们要烧录的文件,因为比特流文件已经生成了吗?他在哪呢?在这个,嗯文件的根目录下, 咱工程文件根目录下,然后选这个 agm 这个文件夹,它就在咱们 agm 这个子文件夹这下边,然后它会生成三个这个 prg, 这个比特流,这三个 prg 的 比特流不一样,就是说咱们如果是说想把这个程序烧到呃 flash 里,就说掉电以后再重新上电,这程序还在,程序不丢失,那就选择第一个 pwm 下杠 master 点 prg, 对吧?用这个 z 泰铢那个口,不要用 a s 口,然后下边这个后边带个 a s 这个,这个是相当于要用这个 a s 那 个接口下载,咱们不用这个, 这个 a s 和这个上面这个 master p r g 这两个文件都是只下到这个 flash 里可以永久保存的。然后下边这个 sram 这个文件, 这个文件是不能烧到 flash 里的,这个文件是直接烧到这个片上这个 sram 这个块里的,这个程序烧了进去之后,你芯片一掉电,这个程序就没有了, 就说咱们一般不都是要烧到 flash 吗?所以说就选这个就行了。用这这 type 口选中这个文件之后,然后这个选项是意思就是说你烧录之前也把你这个片上所有的东西全部给你清空,然后咱们也可以手动进行清空,比如说选这个, 这个就相当于把你 flash 直接全部都给你清空了,当然也可以指定地址清空,那就选这个,对吧? 然后天上地址就可以了,然后底下这些都不用动,基本上就是这个选中这个就是说把比特流烧到这个芯片的 flash 里,或者是指定的位置,然后选这个,就是说烧炉之前先清空,对吧?我一般就是说都不用动,就只需要选这个就可以了, 然后直接点 program, 然后右边就开始跑了,它这个速度很快,当看到这个词条的时候,就说明程序已经烧录成功了,然后这个程序烧录成功之后,咱们连上示波器看一下效果, 对吧?我是五百个周期嘛,我精振是五十兆的,五百个周期得到的这个频率就是一百 k 嘛,一百 k 的 这个放拨程序, 对吧?就这意思, 他这个软件操作起来比较繁琐,主要就是因为他得需要在多个软件里边进行来回操作,就是说倒来倒去的不太方便, 但是芯片还是不错的,感兴趣的话可以大家一起讨论研究一下。好,就这样。

19SSG 03:35查看AI文稿AI文稿

03:35查看AI文稿AI文稿现场可编程门阵列是一种高度灵活的半导体器械,其内部逻辑功能可通过编程进行配置,广泛应用于通信、图像处理、嵌入式系统等领域。 fpga 开发是一个系统化的工程,过程包含了从设计概念到硬件实现的多个阶段。 其核心流程包括需求分析、设计输入功能、仿真逻辑、综合布局、布线、持续分析、板级调试及验证等环节。开发流程起始于需求分析与架构设计,在此阶段,工程师需明确系统的功能、性能指标及外部接口要求, 并基于 fpga 的 资源特性进行架构规划,例如需考虑数据通路的并行性、时钟域划分以及存储资源分配等。这一阶段决定了后续设计的可行性与效率,是项目成功的基础。 接下来进入设计输入阶段,即使用硬件描述语言或高层次综合工具将架构转化为可执行的代码描述, 设计需遵循模块化原则,确保代码的可读性与可重用性。此时设计仅为行为及描述,尚未涉及具体硬件硬设。完成设计输入后,需进行功能仿真,通过仿真工具验证代码的逻辑功能是否符合预期, 测试用力应覆盖正常操作及边界条件。此阶段请关注逻辑正确性,不涉及持续信息,是早期发现设计错误的关键步骤。 通过功能验证后进入逻辑综合阶段,综合工具将 r、 t、 l 代码转换为由 fpga 底层基本逻辑单元构成的网表文件。综合过程中需设置约束条件,如时钟、频率、面积、优化目标等。 综合结果需再次进行仿真,以确认转换未引入功能错误,随后进行布局布线。 这是 fpga 特有的核心环境。铺路只将网表中的逻辑单元映射到芯片的实际物理位置,布线则负责连接这些单元本质,该过程直接影响电路的持续性能与资源利用。逢布局依据持续约束进行优化,力求满足建立时间与保持时间要求。 持续分析贯穿于布局布线之后,通过静态持续分析工具验证设计在目标频率下是否满足所有持续约束。若存在持续为例,需返回修改设计或约束条件,直至达成持续收敛。 持续分析确保电路在物理实现后能稳定运行于指定时钟频率。完成持续验证后生成比特流文件并下载配置至 fpga 器件, 此时进入版级调试与验证阶段。利用逻辑分析仪或片内调试工具实时监测信号,验证系统在实际硬件环境中的功能与性能。此阶段可能发现电源噪声、信号完整性等物理层问题,需迭代调整设计或 pcb 布局, 最后项目交付后仍需进行维护与更新。 fpga 的 优势之一是可重构性,允许通过更新比特流文件修复错误或升级功能不满,这为系统长期氧化提供了灵活性。 总之, fpga 开发是一个多阶段迭代的严谨过程。某强调从行为到物理的逐步细化验证,每个环节相互关联,任意阶段的疏忽都可能导致项目延迟或失败。因此, 熟练掌握流程、工具与方法,秉持模块化设计思维,重仿真与约束管理是高效实现 f p g a。 设计的关键所在。

01:40查看AI文稿AI文稿

01:40查看AI文稿AI文稿朋友们大家好,我是我爱 c 编程,今天我们介绍基于 fpga 的 dct 变换, 下面我们对这个系统进行演示。这里那我们首先点击 run simulation, 点击行为仿真, 然后我们这里设置为五十,点击这个运行,然后我们将数据已有符号时禁止进行显示, 这几个是八个点输入的,八个点的数值我们用红色表示,然后这里是输出, 那么这个结果我们通过 matlab 进行对比,这里我提供了一个 matlab 小 程序,我们这里输入样本跟刚才是一样的。然后点击运行是这么一个结果, 我们可以看到跟 fpga 里面的基本是一致的,当然它中间会存在大量的位宽截取以及量化带来的误差,但是数值的幅度上基本是一样的。 如果为了进一步提高 dct 变换的精度,我们可以将内部的一些处理位宽进行拓展, 从而提高 dct 变换的精度。以上就是整个系统的演示过程。

02:30查看AI文稿AI文稿

02:30查看AI文稿AI文稿图是这样的一个星座图啊,它是四个点,它是四个点啊,这个和你调制的时候有关,调制的时候是四个点,那么它就是这样的一个星座图啊,星座图是这样的啊,那么的话 这个是它的星座图啊,也是它稳态之后的一个星座图啊。 ok, 那 么的话我们这个星座图稳星座图名有了,然后我们的渐向曲线有了,我们依然是这个渐向曲线。 ok, 那 么我们来继续分析啊,我们来继续分析这个, 呃,就进行这个稳态分析。那么在稳态的情况下,我们来看一下它的渐向曲线输出是什么样的?你看当它稳态的时候,这个这个地方,这个 omega 撇它是零,对不对?它是零的时候,这时候 i 加 j q, 但是注意你 i 加 j q, 这时候是有清晰的一个符号的,那么也就是说它实际上是在 我举个例子,比如说是这个符号它落在这个地方,那么你的 i 加 j q 看没有它的相位其实是有一个四分之派的, 也就是说什么呢?也就是说当你在进入一个所谓的稳态的时候,你的渐向的输出其实并不是零, 明白,就这个地方啊,它上面的载波已经被剥离掉以后,纯粹看基带的时候,那么基带进入我的这个渐向器啊,因为它都要渐吗?啊?渐完载波渐渐向吗?啊?大家,当然大家是一起渐的,就是这个基带它其实是会产生一个相差,也就是说我这个地方 会输出一个四分之派啊,如果是这个,呃,这个,如果是这个,你换算成弧度的话,会输出输出一个四分之派的弧度,也就是说,也就是说什么情况呢?也就是说如果你是 qpsk 加我的 argentant 的 这个降噪器的这种形式,其实是没有所谓的稳态的啊,就是稳态。什么?我们指的稳态就是环路降噪器,就是这个,呃,降噪器的这个输出是零,也就是说它其实是没有 稳态的啊。你想想我们现在说所谓的这个稳态需要加个引号,我们在这个稳态的情况下去分析,我们会发现他进入稳态的时候,我的摄像器会输出一个四分制派,那么会输出一个四分制派,就导致一个什么结果呢? 导致我这个时候我的环路认为,我这时候的环路就是环路自己认为没有稳定,他要去调节这个东西,他要往下调,对不对?他要往下调的过程中,这时候 你下一个,因为那个符号变化很快,你下一个符号又来了,那么符号可能会变成这样,变成这样,那么渐向的输出呢?就又变成负的四分之派啊。因为我们要做一个调整,我们算法里面会做一个调整,这个点的象位,我们会把它折算到这个地方啊,就变成了负的四分之派,那么这个地方如果是下一次说这个地方,那么还是四分之。

17yxryudo 03:04查看AI文稿AI文稿

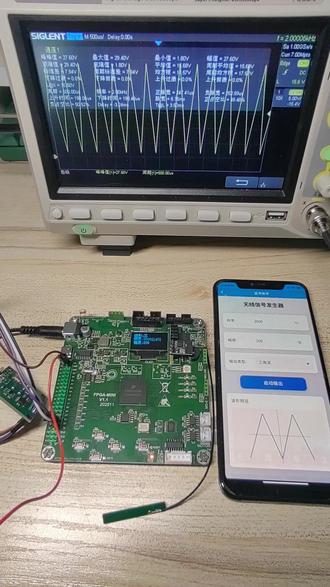

03:04查看AI文稿AI文稿哈喽,大家好,我是零头,接下来我来介绍一下基于 s f b g a 的 无线信号发生器。首先介绍一下按键,这是我们零头设计的,呃, f b g a 的 开发板, 然后这里是一个 oled 屏幕,然后这是一个蓝牙模块,然后这这个的话是一个 dds 模块,里面集成了一个运放,就是用于调节信号的浮值。然后这边的话是我们设计一个 app, 可以 在界面上呃输入频率 幅度,还有一个波形的类型,然后呃 dds 的 输出端是连到的,我们的试播器去查看波形的,现在我们来我们来演示一下功能,首先这边的话可以去输入频率, 然后这边是一个幅度,幅度幅度的等级是零到二五五,然后这边可以去选选择一个波形啊,我们先连接蓝牙吧, 蓝牙连接成功之后,这个灯会快闪,然后我们,嗯,比如说我们现在是一 k, 幅度大一点吧,不然效果不是很明显。好,针旋拨,看,我们已经说出来了,对吧? 看这个频率是九九百九十九点九二,非常准确的一 k, 然后我们把它改变波形的类型吧,比如说我们设置三角波吧,呐,三角波出来了,对吧?然后再是一个方波,呐,方波也出来了, 然后我们改变频率吧,比如说现在是一 k 嘛,我们把它变成十 k, 然后浮值的话变一下变成两百吧,还是方波吧,输出, 你看这个频率就是十 k 了,对吧?呃,这边这边屏幕上也会显示波形的类型,比如说方,表示方波三就是三角波,然后 举就是矩形波嘛,然后还有一个是频率,这个频率的话是写到 d d s 寄存器的一个呃频率的值,但并不是跟我们实际的频频率是一样的,因为它的转化对于 l p g 来说非常复杂, 然后这个幅度的话跟上面是一样的。然后我们现在改变一下波形吧,正弦波,对吧?这个最大是能输到一兆的,我输入一兆吧, 其实这个这个模块不止到一兆,这个模块的话可以到十兆以内 呐,这个是一兆的波形,它的你看频率是一兆,非常准确。嗯,这就是我们所有的功能,谢谢大家。

16零涂科技 09:31查看AI文稿AI文稿

09:31查看AI文稿AI文稿啊,大家好啊,我是五 s 编程,今天我们介绍 gfpga 的 十六 psk 加针同步加卷积编码,加维特比异码同协系统的硬件调试。 首先我们打开工程,打开之后的话,我们可以看到整个系统有这一些模块啊,首先这个的话是十六 psk 调制解调模块,它内部包含了二幺七转接编码,然后调制啊信导模型解调, 然后这个的话是维特比异马,然后这是乌马统计模块,然后这个的话是信号源我们产生啊测试信号进行发射,那这个的话是 vio, 我 们在调试的时候可以通过这个 vio 实时的调成啊信道的信噪比, 然后这是 l a 啊在线采集数据进行显示,好,大概这么一个过程,然后我们对其进行测试,首先对系统进行综合布局布线, 好,这里我们稍微耐心等待一下 这个对,不知道 yes, 好, 然后再产生 beat 文件,点这个图标, 好,然后我们再打开超滑板 下打程序, 然后在这个 vio 这里的话,呃,默认的话是十五。然后我们先从大的猜测,比如说先设置三十个 db 啊,然后在这个地方 点这个加号,选择这个啊数据选项进行触发,设置为 e, 然后在这个地方时间的话随便设一个,比如说七千多就可以了,然后点触发 好,然后我们依次看一下这些信号的含义啊,如果你第一次下载的时候这些波形没有显示的话,比如说我以这个为例,假如说你呃你是第一次烧写,那么它默认是这样的,那你选择 设置为有孵化时间制,然后再啊将这个设置为一百,然后点后的模式 好了,这样就可以看到这个波形了,然后我们依次来介绍这些波形的含义,首先第一个的话是信号比,刚才我们在这个地方设置了三四 d b, 它这里就是三十, 然后这是发射数据源,然后这十六 ps k 映色,那前面这一段的是倒倒平,然后这里的话 l a, 由于资源限制,我加了一个 i ll 的 啊十六 ps k 信号, 然后这是调制之后通过信导之后的啊信号,然后接触端解调节调之后通过一个地通滤波,然后就恢复出数据,然后这个的话进行相关缝提取啊,这个糕点的话就相关缝,我们可以把这糕点放大一点, 可以看到这是一个相关风啊,然后这个的话是根据这个相关风提取定时点我们可以提取啊,导平,使能导平数据,使能数据,最后进行维特比异码啊,对到这一段,然后最后的话就是雾码统计,这里的话每一万个数据统计一次 三十 db 的 时候是雾码是零,然后在这个地方我们会修改下,比如修改为二十 db 啊,再点这个触发 啊,可以看到二十 d 鳄兽一万个出了七个符号啊,带来这一个啊,效果演述完毕,谢谢大家。

19:32查看AI文稿AI文稿

19:32查看AI文稿AI文稿这两天的视频我们一直在更新状态机啊,主要讲的是有线状态机,然后呢?嗯,我们在有线状态机啊,必然会涉及到编码啊,那么我们将几种编码放在一起,就是什么时候用二进制码 啊,什么时候用读热码,什么时候用格为码啊,这是我们之前没有统一说的。 那么这三种编码呢,在逻辑综合中,我们要进行权衡啊,他们有各自的优势啊。那么什么先介绍他们之间有什么区别?那么二进制码是我们最普遍的,最普遍的咱们经常呃,就是首先想到的就是二进制码,那么比如说 这是三位的二进制码,那可以表示八种情况,比如说最开始是零,对吧?零零零,三位啊, 然后是零零一,对吧,然后零零呃,零一零,就是啊,然后是零一一,然后一零零一零一,一零一一,就从零到七,这八种情况,这是我们啊,通常情况下啊,使用的。 那么先最后说一下赌热马,先说格雷马,格雷马如果是三位的话啊,那么他跟, 呃,比如从零开始,他跟二进一码有什么区别呢?你看啊,最开始零零零,然后是零零一啊,序号是一啊,接下来如果是二进一啊,他的序号呃二的话,那么他肯定是零一零,而格雷马呢, 有什么要求呢?他每一次啊,相邻状态仅改变一个比特, 如果像二进制码啊,如果像二进制码,那从零零一,下一个状态就变成零一零,那么相当于零一零,对吧?那么这一位发生变化,这一位发生变化相当于有两位发生变化, 但是格雷马不允许。格雷马的相邻状态就是这零零一跟下一状态仅能变动一个比特,那么我们怎么变呢?嗯就看一眼啊, 那么哎,我让他不变,他不变中间这个量变,嗯,那我再改变呢啊,我让他变成里是不是也只有一个比特再改变呢啊。前面加一个,然后再改变呢? 后面再加啊,这是五啊,这是跟啊,然后再接下来中间这个变成零,然后再接下来啊,就是我们每变一个一次就是跟相邻的状态就仅变动一位,那么这个啊跟二进一码 有什么好处?他通常对于一步数据交互是是可是绝对的首选啊。先记着啊,这是格雷马二斤制马,独乐马呢啊就比较好理解了。其实我们之前举的呃几个例子 好像用的是读热码,咱们看一眼啊,零序号为零啊,然后序号为一啊,就这是八类的啊,这是八类的啊,二三啊四啊五 啊不对六啊七从零总共是八个。从零到七,那么这就是读热码。对于七序号就是一啊,后边是 呃呃八位的啊,一后边后边是七个零啊,如果是六的呢,那就是呃这个为一,后边其他的为为零,嗯其他位为零 啊,那么这就是读热码。读热码呢有什么好处呢?就是每个触发器这是每一个都对应着一个触发器代表了一个状态,逻辑非常简单, 仅啊呃跳转仅需一,你只要判断这一位就行了。只需要一位进行判断 啊,那么这个有什么好处呢?他可能更浪费了处罚器,但是呢他提升了呃 fga 主频的一个最佳力气。那么从这几个呃直观的看你就可以看到哦,二骏骏马和格雷马 的区别啊,然后以及读热,呃读热码的区别,那么如果读热码的呃三位的话,那就是 零零一零一零和一零零,但是在这里举了一个位数比较多的啊,位数比较多的,那么从这块可以看到什么呢?就是呃他的对应的,嗯,就叫福利触发器所需要的数量,比如说我当前的状态 啊,当前状态可以,比如说可以,比如说只有呃状态数量, 如果你只有一位二骏之马,那么要么是零,要么是一,那么你能表达的状态就是零和一,是不是零和一,那么实际上他的状态数量就是二啊,当然这也可以变,对吧?甚至可以到六十四。 好,那么如果是一个仅有一位,仅有一位他能表示的状态数量对于二进制,那么他对啊触发器的需求只要一位, 毫无疑问吗?就就一位吗?零一啊,格力马也是一位。然后呢读热马呢?因为你要表示两个状态,他要么是零一,要么是一零啊,这是简单数, 那么比如说对于刚刚的这八个啊,这是八个毒热码啊,八个毒热码,咱们来看一眼啊,八个毒热码的话,那么你需要的啊触发器就需要八个,因为每一个都存,但是你比较中值比较一位。 而对于啊二金制和格雷格雷马的储发器你是需要什么?三个啊,三个,因为从零零零零零一直到幺幺幺一直可以表现八个状态,而这个毒热马需要八个储发器存储八个啊,对吧?嗯,进行, 呃就是你需要的毒热气要想表现的八个状态的话就需要八个触发器,而对于二进置码和隔离满只需要三个就可以了,所以,所以各有优势,各有缺点。好,那么 咱们统一说一下啊,统一说一下,呃,他们的优势啊,简单说一下,总结说二进置码 他极度节省处罚器是吧?用的处罚器很少, n 个处罚, n 个处罚器可以表示二的 n 次方个状态,比如说刚刚咱们用的是三个处罚器,对吧?三个处罚器,那就可以表表示的是八个状态二的 n 次方,二的三次方 适合什么呢?这种情况适合资源受限的 c p、 l d, 但是它有劣势,什么劣势呢?状态一码逻辑相对复杂,需你既然是逻辑复杂,那么你你你最终用到硬件的时候,你就会需要多级的 l u t, 就是 你进行集连,就是要查超表,进行集连,因为你最终要无论你硬件应应应设到这什么。最后咱们是要看查超表的信息,对吧?那么组合逻辑,你既然他要多集几连,那么就会存在一个延迟,存在一个延迟的 fmax 就较低。一会儿统一说一下,什么叫 f max 啊?好,那么它通常使用的场景呢?就是低速控制的逻辑,你比如说 cpld, 就 属于低速控制的小型气件,小型气件,那么 于此啊,就是比如说格林马,咱们因为只仅有相邻,仅有一位跳动,对吧?那么他有什么优势呢?你会发现哦,他每次仅相对于二骏马,二骏马什么从零零零零零一零一零零一零的时候相应有两位了,但是格林马就相邻,只用一位 跳变,他可以,优势就是极大的降低了翻转的效率,对吧?翻转率,那么,哎,这翻转率就涉及到动态功耗就会怎么样 就减少了,因为你你不需要那么翻转那么多了,对吧?所以可以显,因为你翻的少了,所以可以显著的减少压稳态的风险,因为每翻一次就会有一些压稳态的一个风险出现,那么优势出来了,那这劣势呢? 那那那仅适合次序跳转,呃,就是仅适合顺序跳转较多的状态机,那么随机跳转的会导致就是产生复杂的逻辑,所以呢, 啊,这是格雷马的例式,所以他通常的应用场景是异步的 f i f o 指征设计啊,这个是呃,先进先出的队列,一会会给大家看一下什么叫先进先出的一个队列啊?指征设计还有低功耗的一个系统控制, 那么这是格雷马,那么毒热马咱们刚才也看了,如果想表示八个状态就用八个触发器,那 虽然说他用的确实用的处罚线,他劣势就可以看出来他消耗大量的处罚器,那么,呃,而且就是那他也有优势,他快,他只要比较一位就可以了,所以速度极快, 一码逻辑仅需判断某一位,对吧?完全契合了 f p j l u t f f 的 一个架构,这就是他的优势, 那么劣势就是消耗大量的触发器啊,然后呢,同时呢,非法状态空间就会呃增大,然后需留意单个粒子翻转后的一个安全状态,那个恢复它通常呢,因为它比较 快,所以它的应用场景就是高速接口啊,比如说以太网啊,或者是高性能的 f p j 啊,那么咱们统一的就是简单的说一下这几个编码的一个应用,咱们把这个应用再整合一下,再具体一下,比如说你看应用场景,对于这几种,读热玛、格雷玛、二金制玛,你看 啊,先总的说了一下,读热玛依靠的是极简的一码电路,所以是三百兆赫兹高速设计的 唯一选择,换句话说,你要实现高度,呃,高速设就是高速,呃,设计的话,那你就不要考虑二金置码和格雷码了,就直接是读着码了, 而格雷码呢,是解决时,呃,那个跨时域的一个叫 cd cdc 亚稳态的一个核心武器,多件用于异步的 fi 就是呃, f i f o, 嗯,好,然后但是它是最稳传输,因为仅有一位反转嘛,所以它就是,它是最稳传输。而二金置码呢,它有什么优势?叫最小面积?因为它 在寄存器就是你的硬件资源,尤其寄存器资源极其匮乏的时候,比如说 c p l d, 那 么这时候没有那么多寄存器,你读了吗?要求好多的寄存器,对吧?那没有那么多啊,那么它这时候,哎,它就成为了一个,呃,无奈之举,无奈之举。好, 那么接下来就说一下具体的他们的相关的应用场景啊,为了便于更加清楚的知道啊,他们的就都都用在哪些方面,刚才已经说了高速肯定用的是什么,呃,读热玛, 这就举了一个例子,一百 g 啊,以太网,那么他首选的就是读热玛啊,一百 g 以太网中数据解析逻辑需要三点一纳秒内就决定一个解析状态,换句话说,你如果逻辑非常复杂啊,那么逻辑门就很复杂,就会导致一些持续 持续的失败,是吧?那么所以在这种追求极致速度的情况下,那么就选择啊,选择读热玛 深度分析啊,咱们来看一下为什么这么用呢?一百 g 啊,一一一台网啊,那么这种环境下, f b g a 的 主频通常运行在三二二点二六兆赫兹,这意味着状态机的组合逻辑必须在三点一纳秒上面说了内, 完成从当前状态到下一状态的所有判定,就换句话说,我就要求快啊。那么所以呢,读热码,因为他是一码简单单根连线 综合器呢,只需生成一个极其扁平的一个查找表,避免了多级的一个逻辑嵌套产生的一个路径延迟。 所以啊,这时候你就可以看出,毫无疑问要用读热玛。然后呢,一般认为当状态数量在八到六十四之间,读热玛就通常使用读热玛了,因为他可以保证持续收敛最佳啊,就换句话说,他是首选, 嗯,它保证了 f max 最高主频不会因为这个状啊状态机的复杂度而下降啊,高速啊。那么接下来说的是什么呢? 异步 f r l i o 用的是什么隔离码?我一直没说到底什么叫嗯? f i o 和 f max, 那么 f i o first in first out, 叫先进先出。这如果你学数据结构的话,先进先出的队列,它是一种存储结构,它要求先进去的元素出去的时候先出 啊,那么就是先存入的数据啊,最先被取出啊,呃,举举个例子,比如说它可以用动态的,这是一个队列写出数据,八十九啊,二十五,九十七, 呃,十四啊,呃,是写出这么几个出的时候必须八十九先出,然后二十五,九十七十四,呃,四十四,这就是啊,他的先进先出啊,那么先进先出呢? 这就是一种队列,他可以存数,但是他呃读取啊和存取他的呃顺序是有要求的,那么所以呢,呃,他的作用是数据缓存,解决发送接收率,呃,那个速度的不匹配, 关键点就是异步的 f i i o 是 跨时域传输的一个黄金标准,也是我们常用的,那么 啊,就是 f i o, 然后说一下 f max, 就是 刚刚说的最大工作频率,指电路不发生持续违规前提下运行时最快的频率,那么呃,就记住啊,最大工作频率,这上面咱们涉及到这个案例了,对吧? 这样你们上面说到这个案例,好,那么把这个说完啊,快就用读热码啊,那么,呃隔离码是怎么的?就是最稳定,那么它主要应用的就是什么? e 部的 f i f o 啊,指针同步, 那么因为多时钟与设计中会读取,测试中需要就是 clock right, 需要知道写入测啊, clock right 当前的指征位置来判断它是空还是满啊,这不是指征吗?嗯, 所以呢,如果直接传递二进制指征风险极大。所以为什么我们会用格雷码?因为二进制的三变成四,就是零幺幺变成幺零零,我们涉及到变了三位 啊,但是由于你这个三位一变,貌似逻辑上很简单,但是我们在实际的布线上就会有呃延迟啊,就是因为你 你变,实际上你变得有三个位置发生变化了,布线延迟不同会导致同步器可能抓取的幺幺幺或零零零啊,就是本来应该从零幺幺,然后下一个是幺零零, 但是因为你布线吗?那么你要抓取三个状态,他可能因为他们的食言不通,你抓取的就不是幺零零了,你有可能抓的是幺幺幺,也可能是零零零, 反正就是抓错了。所以隔离码你因为只怎么样跳一位,所以同步器呢?呃,就要么抓到旧值,要么抓到新值,绝不会产生乱码,这也就为什么 e 不 f i i o 指征这个同步的时候,我们用到了隔离码,这是它的一个应用。 还有一个就是我们在课上讲最常用的是二金制码,没有特意强调的,它主要应用在小型的 cpld 中啊,那么尤其是传感器接口的控制器 啊,因为一些简单的控制芯片,比如说低端的啊,芯片中它的储发器资源可能只有几百个,就是换句话说, 资源这么少了,首先不会想到毒热马,因为毒热马就是用到的触发器比较多,所以当你的触发器很少的时候,嗯,首先就不会选择那个毒热马。另外呢,啊, 这个当你实现一个复杂的 spi 读写的时候,要有三十个状态要消耗,呃,如果你是毒热马,就消耗三十个触发器,你总共也没有几个,对吧?但是二进制马呢,只需要五个, 五个从就五个零吗?就可以表示你想五个啊,五个二金制相当于可以表示三十二个位置,也就包含了三十个状态,所以五个储发器就可以实现这个三十个状态的一个 一个负值,对吧?啊,所以这时候啊,就我们会用到二金值吗?啊,因为他可以大大节省了计算器的空间,所以呢, 现代 e d a 工具啊,就已经非常聪明。你说老师,那我到底是,那我到底是用这个用那个,这好几种,你你你,通常现在 e d a 的 工具非常聪明了。呃,对于百分之九十的普通设计,直接用 什么 local parameter 配合工具的 auto 模式啊,它是最佳选择,工具,会根据你的持续余量自动切换。 嗯,你就你用的是 local, 咱们后来如果你们注意到咱们的,呃,状态机的写就状态 表征的时候,咱们用的是 local parameter, 然后你再结合你后期工具的一个 auto 的 一个自动配置,所以它会啊,工具聪明了嘛,就自动去决定啊,自动进行切换。嗯 啊,如果什么情况下涉及到手动干预呢?比如说跨时域啊,传输时指针时强制使用格雷码,或者是主频死活上不去,呃,有些呃,有些状态机处于关键路径,强制使用就强制使用,呃,就是毒热码, 然后呢,或者是资源报错一出,那么这时候就强制使用二进置码。换句话,资源报错强制使用二进置,主频上不去,强制使用读着码啊,跨时域啊,跨 时钟域,传输指向强制用格雷码。好,再次强调了他们主要应用的一个场景啊,这就是,嗯,咱们在状态机中啊常用的三种编码的,呃,解释。

6一路彤行